DECADES: Deeply-Customized Accelerator-Oriented Data Supply Systems Synthesis

Margaret Martonosi Luca Carloni David Wentzlaff

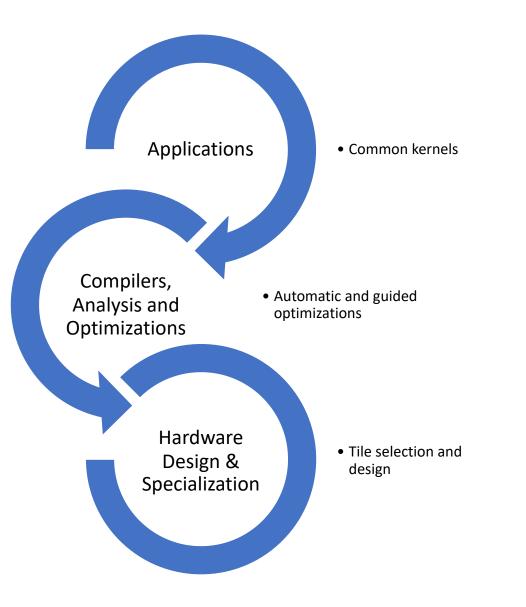

#### DECADES: A VERTICALLY-INTEGRATED APPROACH

Language and Compiler Support

Lead: Martonosi

- Enhance data locality

- Optimize spatial mapping of threads

- Enable in-memory computing

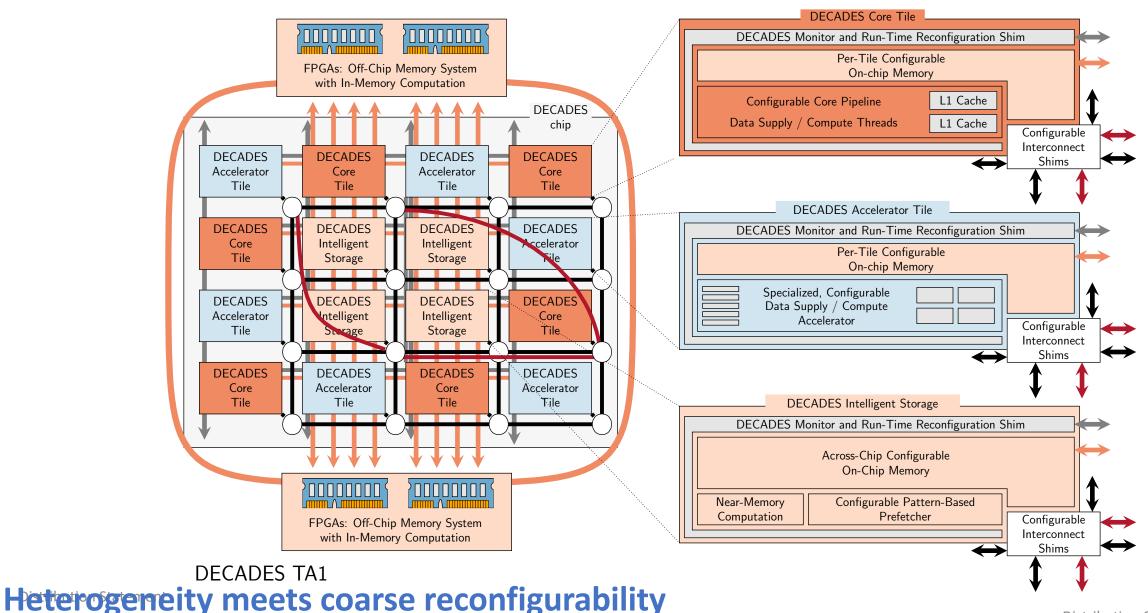

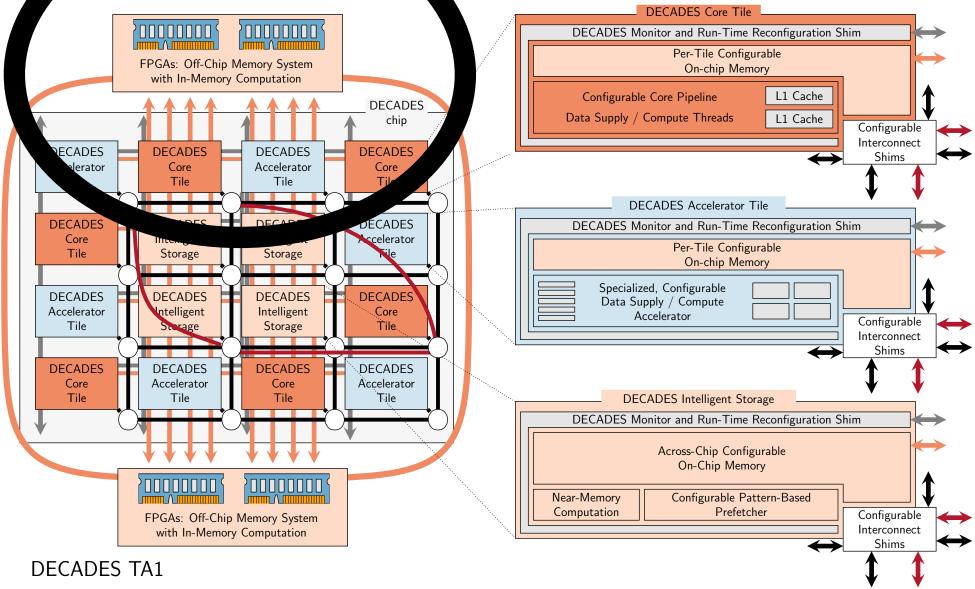

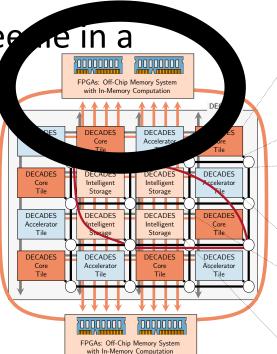

Very Coarse-Grained Reconfigurable Tile-Based Architecture Lead: Carloni

- Coarser than CGRA → VCGRTA

- 3 classes of reconfigurable tiles

- Reconfigurable interconnection network

- Reconfigurable in-memory computing

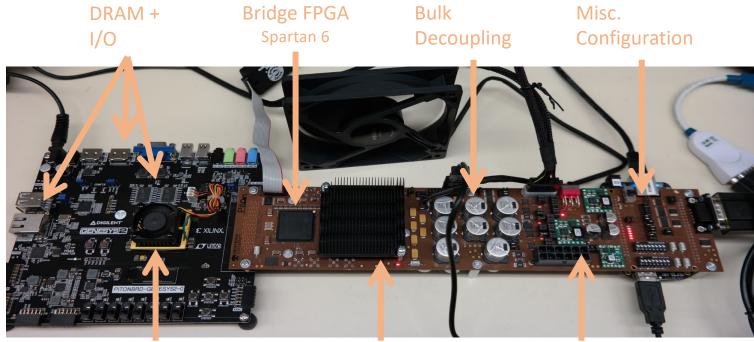

Multi-Tiered Demonstration Strategy

Lead: Wentzlaff

- Scalable full-system simulation

- Multi-FPGA emulation infrastructure

- 225-tile DECADES chip prototype

# DECADES PLATFORM ARCHITECTURE

Distribution C

#### **Project Milestones**

| Task Category                                | Phase 1                                                                    | Phase 2                                                             | Phase 3                                                                                      |

|----------------------------------------------|----------------------------------------------------------------------------|---------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| Language, Compiler &<br>Runtime System (TA2) | 1.1: Initial Design of DECADES<br>Language, Compiler and<br>Runtime System | 2.1: Dynamic Adaptation<br>in DECADES Software<br>Systems           | 3.1: Full Static/Dynamic<br>Optimization in DECADES<br>Language, Compiler, Runtime<br>SYstem |

| Application<br>Development (TA1,<br>TA2)     | 1.2: Transformation of Provided<br>Benchmarks                              | 2.2: Optimization of Provided<br>Benchmarks                         | 3.2: Full benchmark<br>characterization on DECADES<br>Hardware                               |

| Platform Architecture (TA2, TA2)             | 1.3: Initial Design of DECADES<br>Platform Architecture                    | 2.3: Full Design of DECADES<br>Platform Architecture                | 3.3: Optimization and Scaling of<br>DECADES Platform Architecture                            |

| Simulation and<br>Emulation (TA1, TA2)       | 1.4: Lightweight Simulator and<br>Emulator for DECADES Platform            | 2.4: Full-system Simulator and<br>Emulator for DECADES Platform     | 3.4: Scalable Multi-FPGA-Based<br>Emulator for DECADES Platform                              |

| Hardware Design (TA1)                        | 1.5: Test chip development                                                 | 2.5: DECADES Chip design                                            | 3.5: Full Hardware System<br>Demonstration                                                   |

| Technology Transfer<br>(TA1, TA2)            | 1.6: Transfer of Phase 1 Results and Deliverables                          | 2.6: Transfer of Phase 1 and<br>Phase 2 Results and<br>Deliverables | 3.6: Transfer of Results and<br>Deliverables from all three phases<br>4 Distribution C       |

4

# This Talk

- Compiler and Chip Development

- Other Research Status Updates

#### Status & Approach

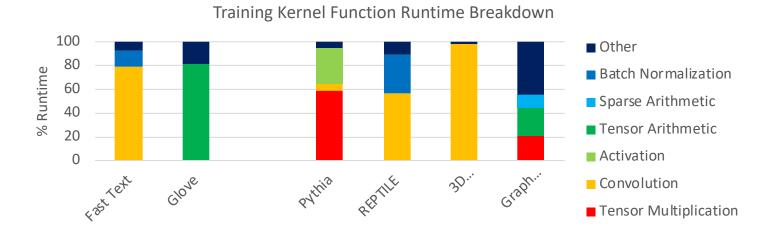

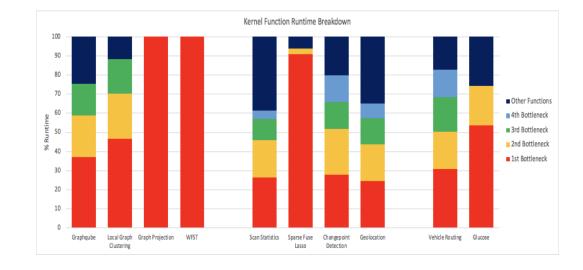

## Application Profiling: Data -> Design Plans

Inference Kernel Function Runtime Breakdown 100 Other 80 % Runtime Batch Normalization 60 Sparse Arithmetic 40 Tensor Arithmetic 20 Activation 0 30<sup>...</sup> Fastlet Pythia REPTILE Convolution Tensor Multiplication

Graph (C/C++)

Graph (Python)

Combinatorics (C/C++)

### Applications Mapping to DECADES

|                        | DECADES features for acceleration |                  |                 |                    |            |                   |                |                             |                           |                                |                                         |                                           |                           |

|------------------------|-----------------------------------|------------------|-----------------|--------------------|------------|-------------------|----------------|-----------------------------|---------------------------|--------------------------------|-----------------------------------------|-------------------------------------------|---------------------------|

|                        |                                   | Accelerator tile |                 |                    |            |                   |                | Memory tile                 |                           |                                |                                         | Processor tile                            |                           |

|                        | convoluti<br>on                   | vector<br>arith  | matrix<br>arith | graph<br>utilities | statistics | SOCP<br>equations | map<br>/reduce | efficient data<br>streaming | prefetching<br>graph data | prefetching<br>SAT<br>formulas | temp data for inter<br>accelerator comm | in-memory /<br>near-memory<br>computation | prefetching<br>graph data |

| 3D segmentation        | Х                                 |                  |                 |                    |            |                   |                | Х                           |                           |                                |                                         |                                           |                           |

| Pythia                 | Х                                 | Х                | Х               |                    |            |                   |                | Х                           |                           |                                |                                         |                                           |                           |

| Text classification    |                                   | Х                | Х               |                    |            |                   |                |                             |                           |                                |                                         | Х                                         |                           |

| Glove                  |                                   | Х                |                 |                    |            |                   |                | Х                           |                           |                                |                                         |                                           |                           |

| Reptile                | Х                                 | Х                |                 |                    |            |                   |                | Х                           |                           |                                |                                         |                                           |                           |

| Vehicle routing        |                                   |                  |                 |                    |            |                   |                |                             |                           |                                |                                         |                                           | Х                         |

| Geolocation            |                                   | Х                |                 |                    |            |                   | Х              |                             |                           |                                | X                                       |                                           |                           |

| Scan statistics        |                                   |                  |                 |                    | Х          |                   |                |                             | Х                         |                                |                                         | Х                                         |                           |

| Local graph clustering |                                   |                  |                 | Х                  |            |                   |                |                             | Х                         |                                |                                         |                                           |                           |

| Sparse fused lasso     |                                   |                  |                 |                    |            | Х                 |                |                             | Х                         |                                |                                         |                                           | Х                         |

| Graph projections      |                                   |                  |                 |                    |            |                   |                |                             | Х                         |                                |                                         | Х                                         |                           |

| Graph classification   |                                   | Х                | Х               |                    |            |                   |                |                             |                           |                                |                                         |                                           |                           |

| WFST                   |                                   |                  |                 |                    |            |                   |                |                             | Х                         |                                |                                         | Х                                         |                           |

| Glucose                |                                   |                  |                 |                    |            |                   |                |                             |                           | Х                              |                                         |                                           |                           |

| Graph query-by-example |                                   |                  |                 | Х                  |            |                   |                |                             | Х                         |                                |                                         | Х                                         |                           |

| Changepoint detection  |                                   |                  |                 |                    | Х          |                   |                |                             | Х                         |                                |                                         | Х                                         |                           |

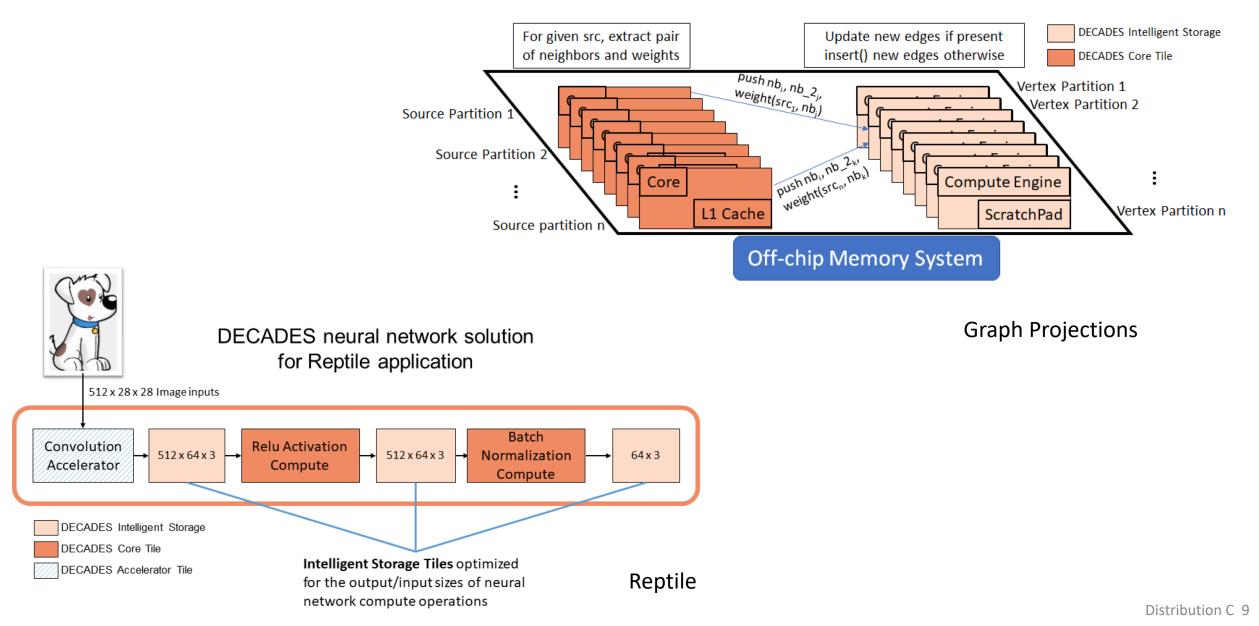

# Example Mappings to DECADES

## This Talk

- Compiler and Chip Development

- Other Research Status Updates

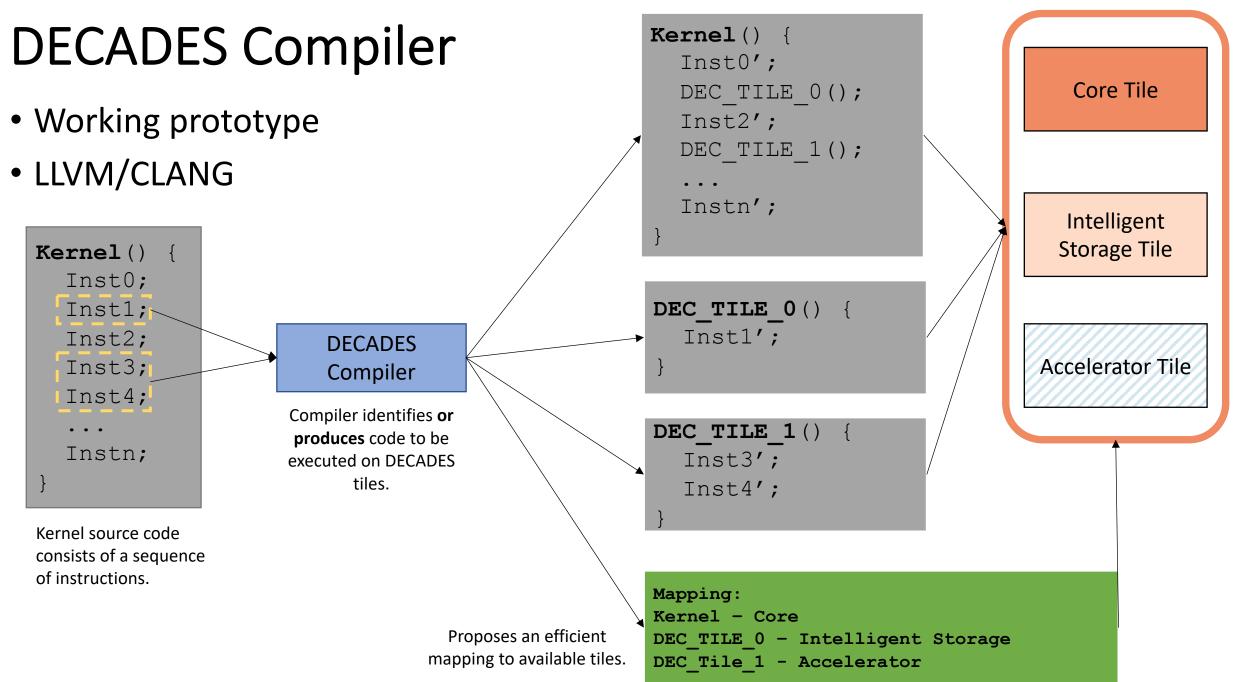

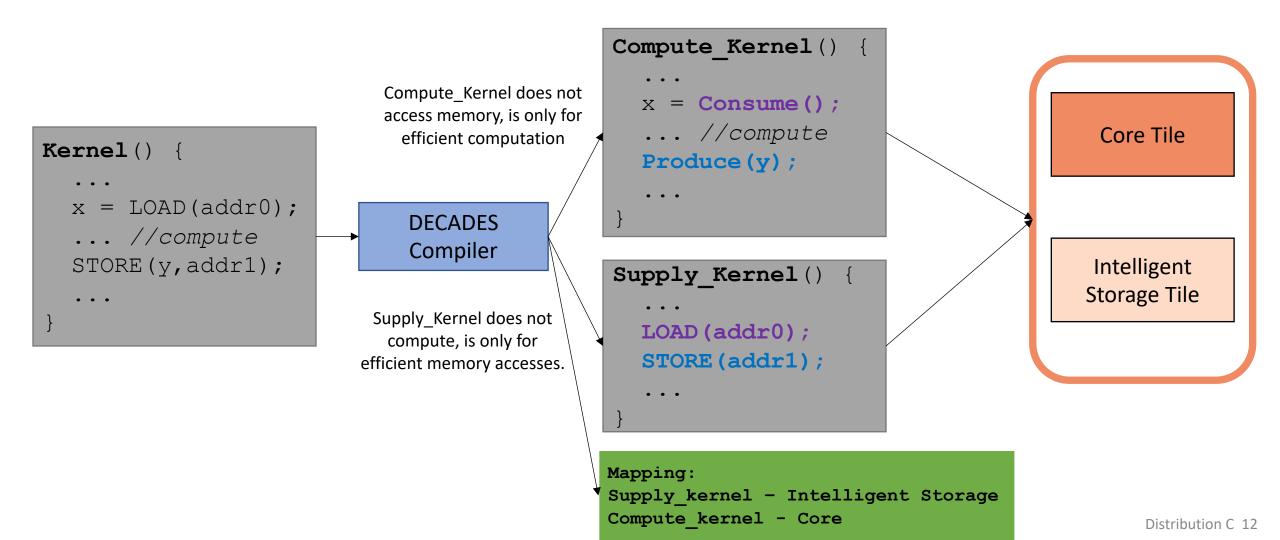

#### DECADES Compiler: Decoupling Supply/Compute

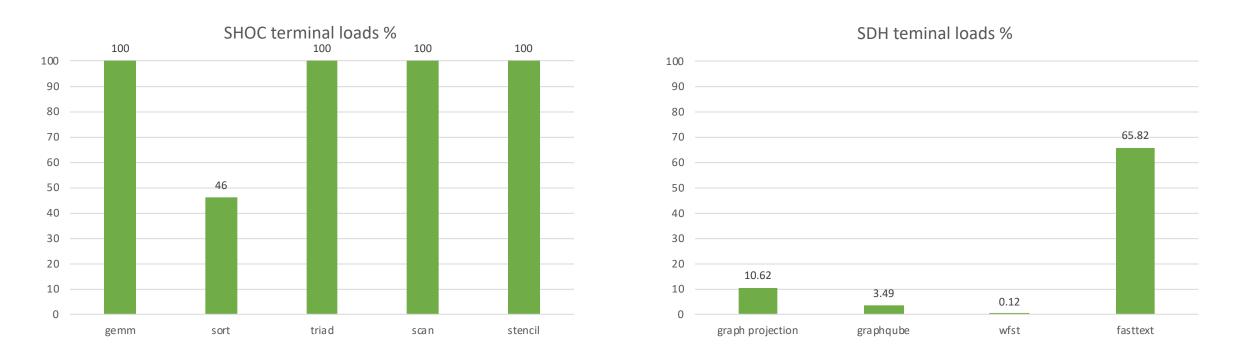

Implemented in DECADES Clang/LLVM based compiler Can automatically decouple SHOC, Parboil microbenchmarks, WFST, Graph Projections, Graphqube, FastText

# Terminal Loads & Decoupled Supply-Compute

- SDH apps have fewer *Terminal loads (*load for which supply kernel does not need load return values) than SHOC

- => Decouple at a coarser granularity:

- Do not decouple all memory operations, allowing Supply\_Kernel to have more *terminal loads* and execute sufficiently ahead of Compute Kernel.

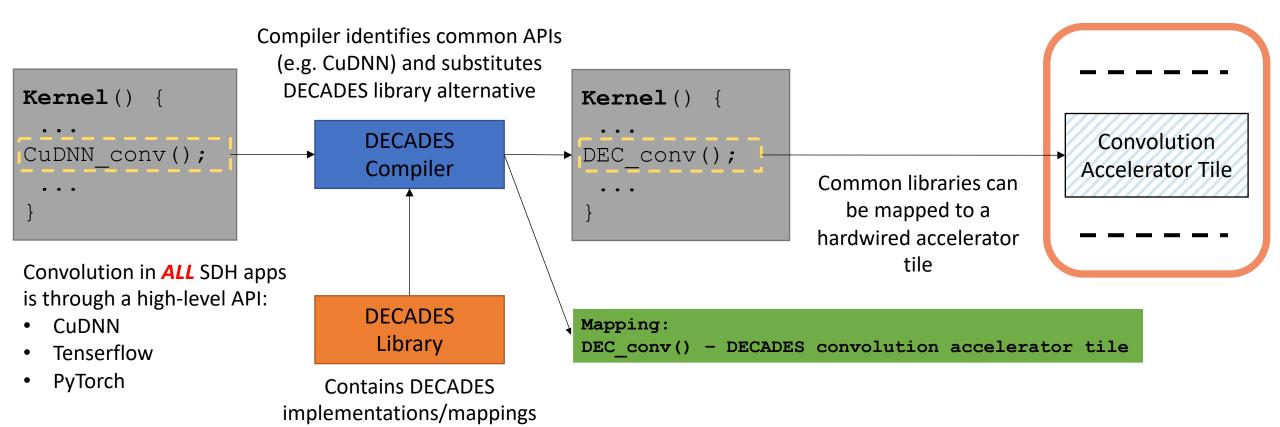

# **DECADES Library Interfaces**

- Building up DECADES library and API

- Program annotations +

- Efficient implementations/mappings of common kernels. e.g., convolution.

- Map to accelerator tile + memory wrappers

#### **Project Milestones**

| Phase 1                                                                                                | Phase 2                                                                                                                                                                                                                                                                                                                                                                            | Phase 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul><li>1.1: Initial Design of DECADES</li><li>Language, Compiler and</li><li>Runtime System</li></ul> | 2.1: Dynamic Adaptation<br>in DECADES Software<br>Systems                                                                                                                                                                                                                                                                                                                          | 3.1: Full Static/Dynamic<br>Optimization in DECADES<br>Language, Compiler, Runtime<br>SYstem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 1.2: Transformation of Provided<br>Benchmarks                                                          | 2.2: Optimization of Provided<br>Benchmarks                                                                                                                                                                                                                                                                                                                                        | 3.2: Full benchmark<br>characterization on DECADES<br>Hardware                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 1.3: Initial Design of DECADES<br>Platform Architecture                                                | 2.3: Full Design of DECADES<br>Platform Architecture                                                                                                                                                                                                                                                                                                                               | 3.3: Optimization and Scaling of<br>DECADES Platform Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 1.4: Lightweight Simulator and<br>Emulator for DECADES Platform                                        | 2.4: Full-system Simulator and<br>Emulator for DECADES Platform                                                                                                                                                                                                                                                                                                                    | 3.4: Scalable Multi-FPGA-Based<br>Emulator for DECADES Platform                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 1.5: Test chip development                                                                             | 2.5: DECADES Chip design                                                                                                                                                                                                                                                                                                                                                           | 3.5: Full Hardware System<br>Demonstration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 1.6. Transfer of Phase 1 Results<br>and Deliverables                                                   | 2.6: Transfer of Phase 1 and<br>Phase 2 Results and<br>Deliverables                                                                                                                                                                                                                                                                                                                | 3.6: Transfer of Results and Deliverables from all three phases                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                        | <ul> <li>1.1: Initial Design of DECADES<br/>Language, Compiler and<br/>Runtime System</li> <li>1.2: Transformation of Provided<br/>Benchmarks</li> <li>1.3: Initial Design of DECADES<br/>Platform Architecture</li> <li>1.4: Lightweight Simulator and<br/>Emulator for DECADES Platform</li> <li>1.5: Test chip development</li> <li>1.6. Transfer of Phase 1 Results</li> </ul> | 1.1: Initial Design of DECADES<br>Language, Compiler and<br>Runtime System2.1: Dynamic Adaptation<br>in DECADES Software<br>Systems1.2: Transformation of Provided<br>Benchmarks2.2: Optimization of Provided<br>Benchmarks1.3: Initial Design of DECADES<br>Platform Architecture2.3: Full Design of DECADES<br>Platform Architecture1.4: Liphtweight Simulator and<br>Emulator for DECADES Platform2.4: Full-system Simulator and<br>Emulator for DECADES Platform1.5: Test chip development2.5: DECADES Chip design1.6. Transfer of Phase 1 Nesults<br>and Deliverables2.6: Transfer of Phase 1 and<br>Phase 2 Results and |

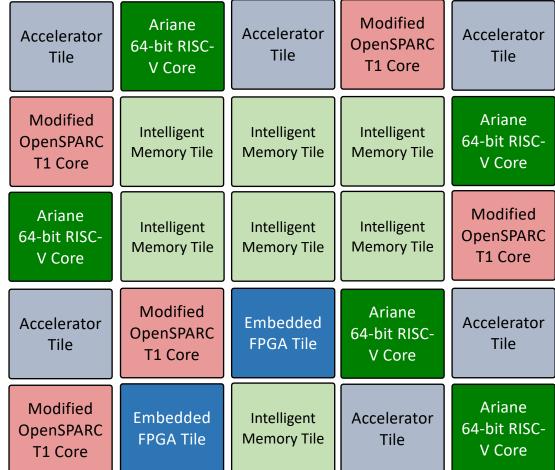

# Planned DECADES Test Chip: Early 2020

- 9mm2 GF 14nm

- Sample of tiles

- Heterogeneous CPUs

- Tiles connected with multi-plane on-chip 2D Mesh network

- Intelligent memory tiles support optimized inter-tile data movement

Off Chip Memory System with In-Memory Computation implemented in FPGA

# DECADES Test Chip: CPU Heterogeneity

- Heterogeneity enables matching performance/energy profile to application phase

- DECADES Mixture of three core type

- OpenSPARC T1 multithreaded core

- Multithreaded efficiency

- Full Stack OS

- Ariane 64-bit RISC-V core

- Decent performance 64-bit core

- PicoRV32 32-bit RISC-V microcontroller

- Area and Power-efficient/Low performance core drives intelligent storage

- Specialized accelerator tiles

- Ex: Convolution accelerator

- All cores and accelerators use common DECADES memory system with orchestrated data movement

- Leverage JuxtaPiton Expertise: Open-source, general-purpose, heterogeneous-ISA processor

- Shared memory between 64-bit OpenSPARC T1 and 32-bit PicoRV32 cores

- Boots Linux on OpenSPARC T1, offloads 32-bit RISC-V binaries to low-power PicoRV32 core

## This Talk

- Compiler and Chip Development

- Other Research Status Updates

# DECADES PLATFORM ARCHITECTURE

Distribution C 19

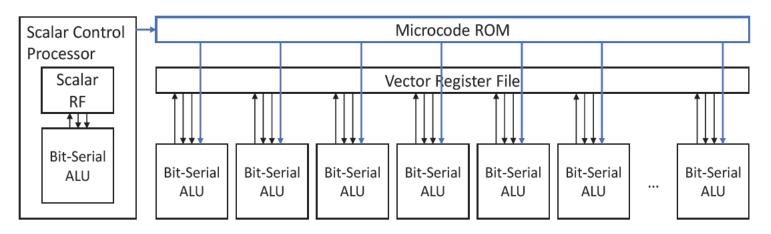

#### **Bit-Serial SIMD**

- Bit-Serial: Calculations on bit-level instead of word-level

- Similar to breaking instructions into micro-operations

- Dramatic reduction in datapath hardware

- Overhead in latency and control logic

- Bit-Serial SIMD Exploit efficient datapath

- Can fit many ALUs in a small area

- Enable very wide SIMD parallelism exploit data-level parallelism

- Mitigate latency overhead by improving throughput

- Minimize control logic overhead

- Energy-efficient

#### [Jackson & Wentzlaff]

# Bit-Serial SIMD->Near-Memory Compute in DECADES

- <u>Goal</u>: Minimize data movement between memory and core by performing computation close to memory

- **Opportunity**: Small per-element computation on large data structure

- FastText

- Glucose

- <u>Opportunity</u>: Searching through large structures (finding a neglice in a haystack)

- Graphqube

- MapReduce

- Graph Projection

- <u>Opportunity</u>: Large numbers of indirect references

- Glucose

- BFS

sön & Wentzlaff]

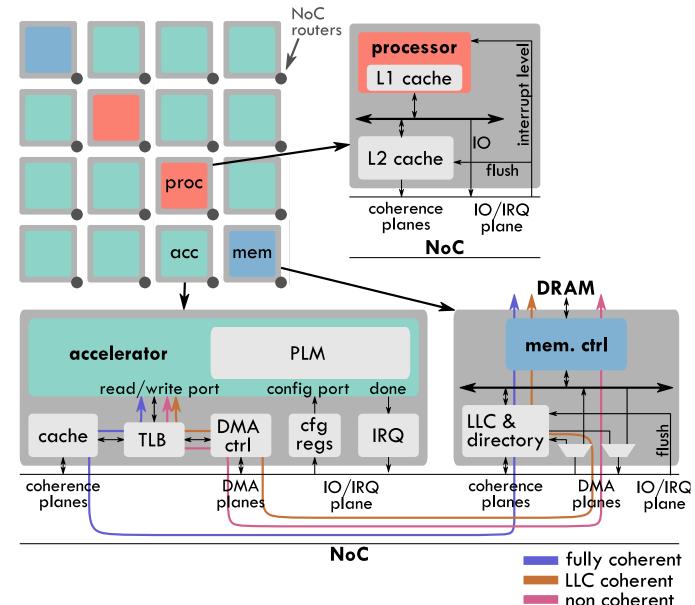

## Accelerator Integration in DECADES Architectures

How are accelerators integrated in the DECADES architecture?

- Hardware Integration

- Reconfigurable interface socket

- Software Integration

- Invocation and (re)-configuration through Linux device drivers

- Interaction with Memory Hierarchy

- Support for coexistence of 3 main heterogeneous coherence models

- Run-time algorithm to select the optimal coherence model at each accelerator invocation

#### Publications: [Giri et al., IEEE Micro'18] [Giri et al., NOCS'18] [Giri et al., ASPDAC'19]

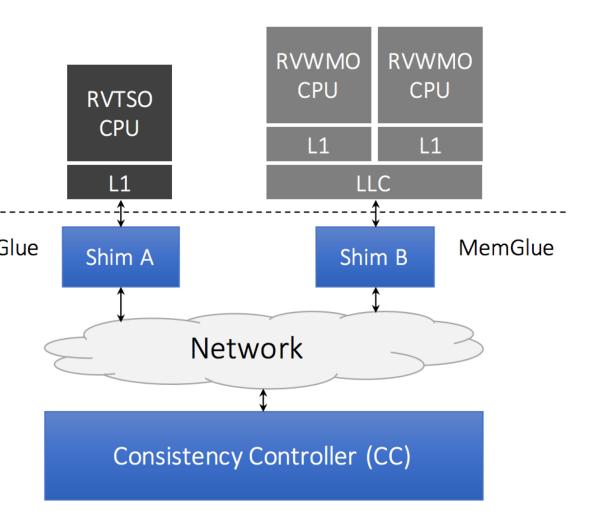

#### Integrating Heterogeneous CPUs and Memory Consistency Models

- Increasing heterogeneous parallelism → challenging to integrate hardware with heterogeneous memory models

- Key insight: hardware generally wants to support high-level language programs, e.g. C/C++

- MemGlue approach:

- Consistency protocol designed to enforce C/C++ MCM requirements for a heterogeneously parallel system with minimal added hardware

- Enables fine-grained communication between heterogeneous system components

Off Chip Memory System with In-Memory Computation implemented in FPGA

#### [Trippel, Manocha & Martonosi]

## MemGlue Consistency/Coherence Shims

- Heterogeneous cluster (i.e. cluster) accelerators which share a localize

- MemGlue integrates clusters with

- Consistency shims (i.e. shims) per-cli outside memory system

- Consistency controller (i.e. CC) to int MemGlue

#### MemGlue Status and Performance Expectations

- Baseline MemGlue:

- Timestamps (ts) instead of invalidation messages → eliminates traffic due to invalidations

- Minimal storage requirements → ts for each cache line in the LLC of each cluster; sharer list in the CC

- MemGlue exploration and optimizations:

- Explore methods for sending writes to CC only at sync point → minimize update traffic

- Explore optimal buffer size  $\rightarrow$  minimize traffic due to full shim buffers

- Performance expectation: achieve heterogeneous consistency performance approx. equal to the performance of the cluster with the strongest MCM

- Other goals: prove MemGlue properties using formal techniques

## **Project Milestones**

| Task Category                             | Phase 1                                                                    | Phase 2                                                             | Phase 3                                                                                      |  |

|-------------------------------------------|----------------------------------------------------------------------------|---------------------------------------------------------------------|----------------------------------------------------------------------------------------------|--|

| Language, Compiler & Runtime System (TA2) | 1.1: Initial Design of DECADES<br>Language, Compiler and<br>Runtime System | 2.1: Dynamic Adaptation<br>in DECADES Software<br>Systems           | 3.1: Full Static/Dynamic<br>Optimization in DECADES<br>Language, Compiler, Runtime<br>SYstem |  |

| Application<br>Development (TA1,<br>TA2)  | 1.2: Transformation of Provided<br>Benchmarks                              | 2.2: Optimization of Provided<br>Benchmarks                         | 3.2: Full benchmark<br>characterization on DECADES<br>Hardware                               |  |

| Platform Architecture (TA2, TA2)          | 1.3: Initial Design of DECADES<br>Platform Architecture                    | 2.3: Full Design of DECADES<br>Platform Architecture                | 3.3: Optimization and Scaling of<br>DECADES Platform Architecture                            |  |

| Simulation and<br>Emulation (TA1, TA2)    | 1.4: Lightweight Simulator and<br>Emulator for DECADES Platform            | 2.4: Full-system Simulator and<br>Emulator for DECADES Platform     | 3.4: Scalable Multi-FPGA-Based<br>Emulator for DECADES Platform                              |  |

| Hardware Design (TA1)                     | 1.5: Test chin development                                                 | 2.5: DECADES Chip design                                            | 3.5: Full Hardware System<br>Demonstration                                                   |  |

| Technology Transfer<br>(TA1, TA2)         | 1.6: Transfer of Phase 1 Results and Deliverables                          | 2.6: Transfer of Phase 1 and<br>Phase 2 Results and<br>Deliverables | 3.6: Transfer of Results and Deliverables from all three phases                              |  |

# **Technology Transfer Plans & Status**

- Outputs:

- Software ecosystem

- Chip design

- FPGA emulation system

- Status:

- Moved OpenPiton to github

- Released two versions of OpenPiton

- Support for JuxtaPiton (PicoRV32)

- Support for Ariane (64-bit RISC-V core)

- QEMU Instrumentation Plane

- Before July 1:

- DECADES Compiler + Pythia Simulator

- One more OpenPiton release

Chipset FPGA Kintex 7

Test Chip + Heat Sink Power Supply

#### Conclusions

- Compiler:

- Working prototype with ongoing feature additions

- Hardware:

- Several tile designs ready. More soon.

- Simulation/Emulation:

- Lightweight simulator: Pythia

- QEMU Instrumentation plane

- FPGA Emulation